A SystemVerilog reimplementation of the 3dfx Voodoo Graphics GPU for FPGA.

This project implements the complete Voodoo 1 3D graphics pipeline in synthesizable RTL. The implementation is based on analysis of the original hardware specifications and the PCem emulator's Voodoo emulation code.

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| Voodoo variant | Voodoo 1 (SST-1) only |

| Pipeline | Highly pipelined: rasterizer → TMU (32-stage) → pixel shader (10-stage) → depth buffer (3-stage) → framebuffer (3-stage), valid/ready handshaking with inter-stage FIFOs |

| FPGA target | ULX3S (Lattice ECP5 LFE5U-85F, 32MB SDRAM) |

| Display | VGA display controller with SDRAM prefetch buffer |

| Language | SystemVerilog |

| Code size | ~18,000 lines, 20+ RTL modules |

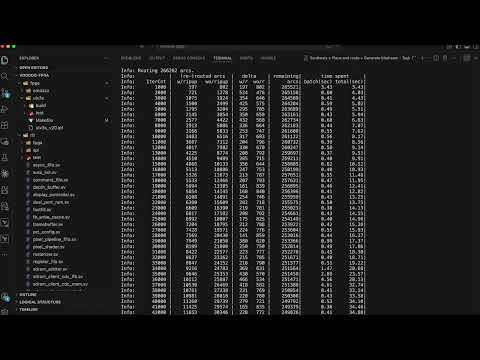

| Synthesis | Open-source toolchain (Yosys, yosys-slang, nextpnr-ecp5) |

| Verification | Verilator testbenches, Glide trace replay, PCem bridge for real-time verification |

| Clocks | 25.175 MHz VGA output, 50 MHz render pipeline, 100 MHz SDRAM subsystem with per-client CDC bridges. Timing closure achieved through deep pipelining, basic floorplanning, etc. |

| Memory subsystem | Custom SDRAM controller, 7-client arbiter with bank interleaving, 4-level cache hierarchy (texture, depth, FB write-combining, FB read) |

| FPGA resources | 68% LUTs, 38% FFs, 37% BRAM, 70% DSP (ECP5-85F) |

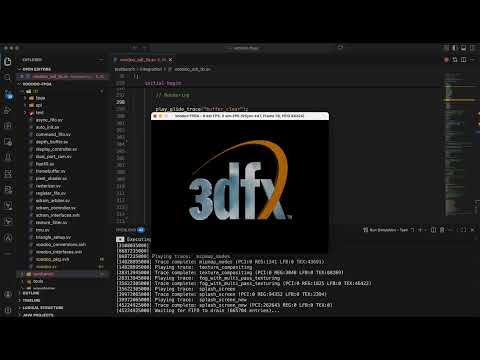

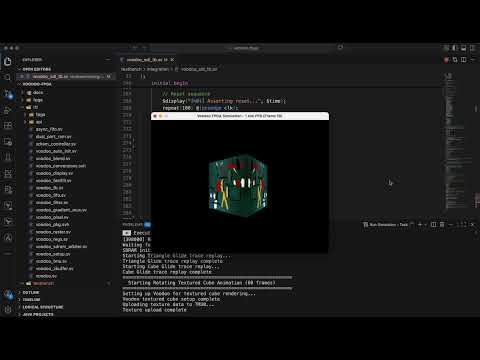

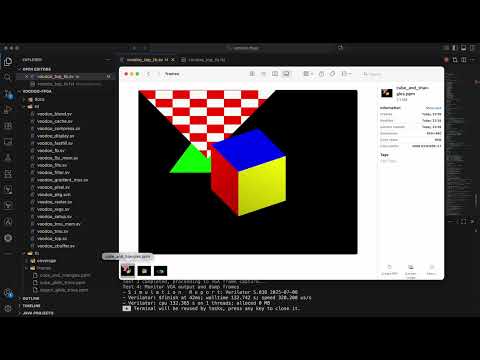

The design is verified using Verilator. A PCem bridge testbench connects the RTL to PCem over shared memory, replacing its software Voodoo emulation with the RTL design. This allows real Glide 2.x games running inside PCem to drive the hardware simulation and display rendered output via SDL in real time.

Started in August 2025. First 3D render (teapot) in October 2025. Valley of Ra demo and Unreal Tournament running in February 2026. ECP5-85F synthesis and place-and-route with timing closure at 50/100 MHz in March 2026.

Work in progress. The 3D rendering pipeline is functional and runs Glide 2.x games correctly in simulation. FPGA synthesis and place-and-route are complete, host to FPGA transport implementation and hardware testing are the next steps.

All code written by Claude Code.

This is not an open source project. The source code is not publicly available.

3dfx, Voodoo, and Glide are trademarks of 3dfx Interactive, Inc., now owned by Nvidia Corporation. This project is not affiliated with or endorsed by Nvidia. All other trademarks are the property of their respective owners. This is an independent reimplementation for educational and hobbyist purposes.